Pentium II 处理器,是对我影响最大的一款 CPU。从对电脑的一头雾水,到半夜爬起来捂着 Modem(因为拨号的声音...)上网,实达蓝天白云 939 之奔二 350 ,是我的启蒙老师。在那台奔二上玩了星际争霸、盟军敢死队、帝国时代、魔法门之英雄无敌3,学过3D Max 2.5、VisualBasic,上过 yahoo!、搜狐、深圳之窗、whitehouse.com(不是 gov!)、aisex.com、blogcn.com,甚至学会了在 BIOS 里把 100MHz 外频超到 112MHz 幻想赶超赛扬 300A 的神迹……一切一切基于电脑的懵懂回忆,都来源于奔二。

屡次搬家之后,父母嫌 99 年买的老电脑占地方,要扔。临扔前帮我拍下了原装 CPU 最后的模样。

也是从这张图我才确认,后来从闲鱼淘的奔二是个拼装货。

铭牌:350/512/100/2.0V S1

19040247-0162 Philippines

i (m)(c) '97 SL356

时隔20年,看着桌上摞起来越来越多的 Socket 或 LGA(平面网格阵列)的CPU,想起 Slot 1 封装的奔二不论在当年还是现代都富有特色,于是想买一块研究研究。闲鱼 35 块包邮到手,可惜外壳是奔三 550 的拼装货不提也罢。

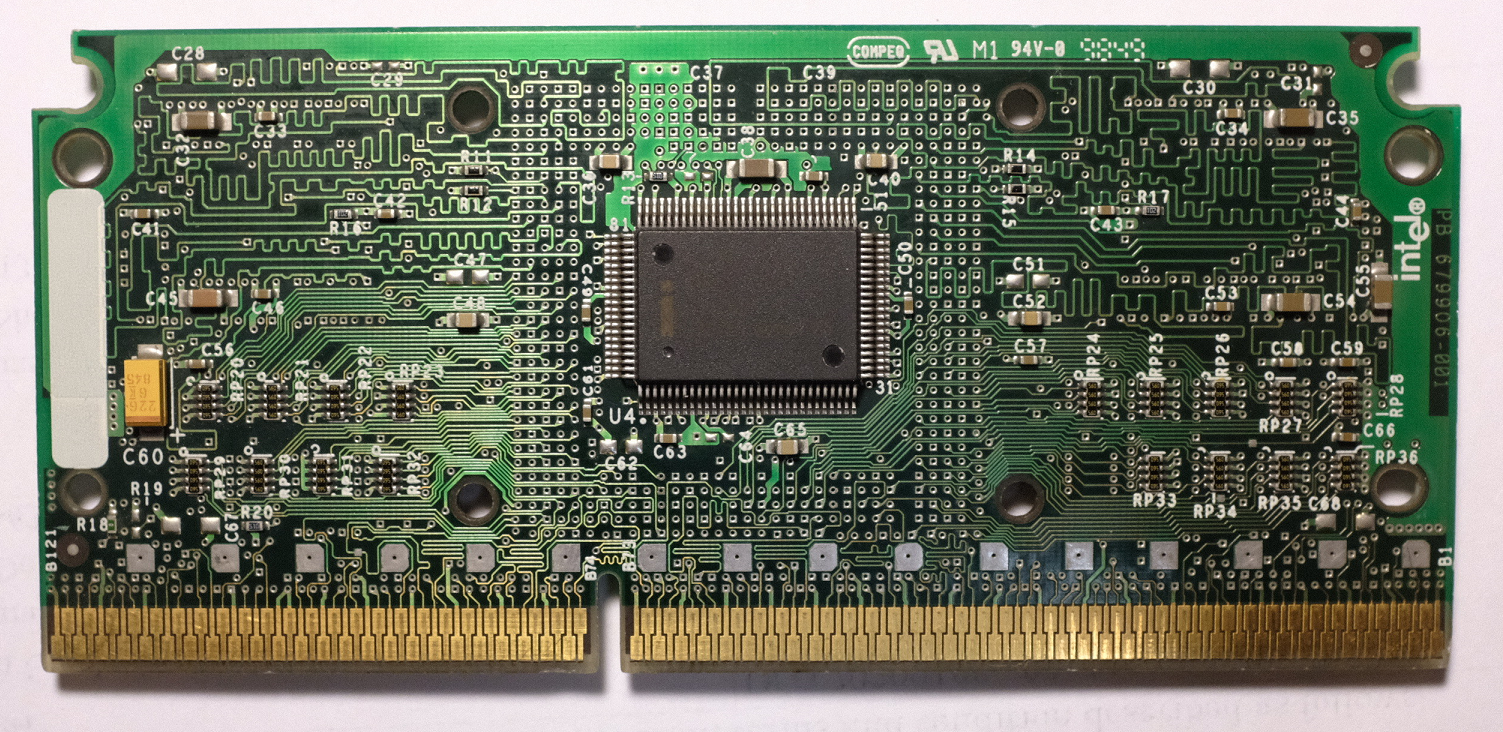

上图中间黑色 SOP 封装芯片为 tag sram,为二级缓存提供 tag 存储

tag sram 的激光刻字:S82459AD

8851PZ44

SL2WF

INTEL (m)(c) '95

由于丢失了原装外壳,闲鱼的这颗奔二无法确定内部频率,只是看 Cache 的布局,应该还是 Deschutes 架构的奔二,和曾经的启蒙奔二同属一系。

Pentium II 和 Pentium III 信息对照:

| 型号 | 架构 | 制程 | Cache | 时钟 | 推出时间 | 封装 |

|---|---|---|---|---|---|---|

| Pentium II | Klamath | 350 | L1+半速 L2 | 233-300 (66MHz FSB) | 1997H1 | Slot 1 |

| Deschutes | 250 | L1+半速 L2 | 266-333 (66MHz FSB) | 1998H1 | Slot 1 | |

| Deschutes | 250 | L1+半速 L2 | 350-450 (100MHz FSB) | 1998H1 | Slot 1 | |

| Pentium III | Katmai | 250 | L1+半速 L2 | 450-600 (100MHz FSB) | 1999H1 | Slot 1 |

| Katmai | 250 | L1+半速 L2 | 533, 600 (133MHz FSB) | 1999H1 | Slot 1 | |

| Coppermine | 180 | L1+全速 L2 | 550-1100 (100MHz FSB) | 1999H2 | Slot 1/Socket 370 | |

| Coppermine | 180 | L1+全速 L2 | 533-1133 (133MHz FSB) | 1999H2 | Slot 1/Socket 370 | |

| Coppermine T | 180 | L1+全速 L2 | 800-1133 (133MHz FSB) | 2000H2 | Socket 370 | |

| Tualatin | 130 | L1+全速 L2 | 1000-1400 (133MHz FSB) | 2001H2 | Socket 370 |

其中,从 Slot 1 更换到 Socket 370 的过程中,还存在一段时间过渡期,使得 socket-slot 转接板大行其道。更替的原因,据 wiki 说是由于 1GHz 以上的插卡电路频率已达极限。

至于 Tualatin,中文称之为「图拉丁」,更是成为一代神话,至今「图吧垃圾佬」仍是一个为 DIYer 们喜闻乐见的称呼。有道是:

三千预算进「卡吧」,加钱加到九万八。

三千预算进「图吧」,小学对面开网吧。

正式来学习一下 Pentium II 的硬件设计。

正面图

卡片正面中间是芯片核心,凉飕飕的铝制散热壳刷好硅胶后与更大的散热鳍片和散热风扇直接接触。左右两侧两片相同规格的 SRAM 芯片,为芯片提供半速二级缓存(每两个 FSB 时钟存取一次)。芯片spec 显示,其存储结构为 64K 行 * 36 bits 的存储阵列(比 256KB 稍多一点),最高工作时钟 250MHz,这也就是半速二级缓存的原因了。另外淘宝显示,该芯片目前价格为单颗一块钱多点。

尝试拆掉散热铝壳露出核心,失败,看起来并不是胶粘,而是锡球焊接——这样也才说得过去。

背面图

背面唯一的芯片是打了 Intel 标记和芯片代号的 tag SRAM,不过国内外网上发了疯找也没找到芯片 spec ......

Tag SRAM 的作用,在 这里 讲得非常好,图文并茂,讲清了所有 cache 类型的查找替换方法。为了避免网页失效,在此简单复述一种典型的 cache 使用思路。

cache 是按 字节寻址 的同步存储器,几乎所有的 cache 都使用 SRAM,甚至寄存器作为物理介质。

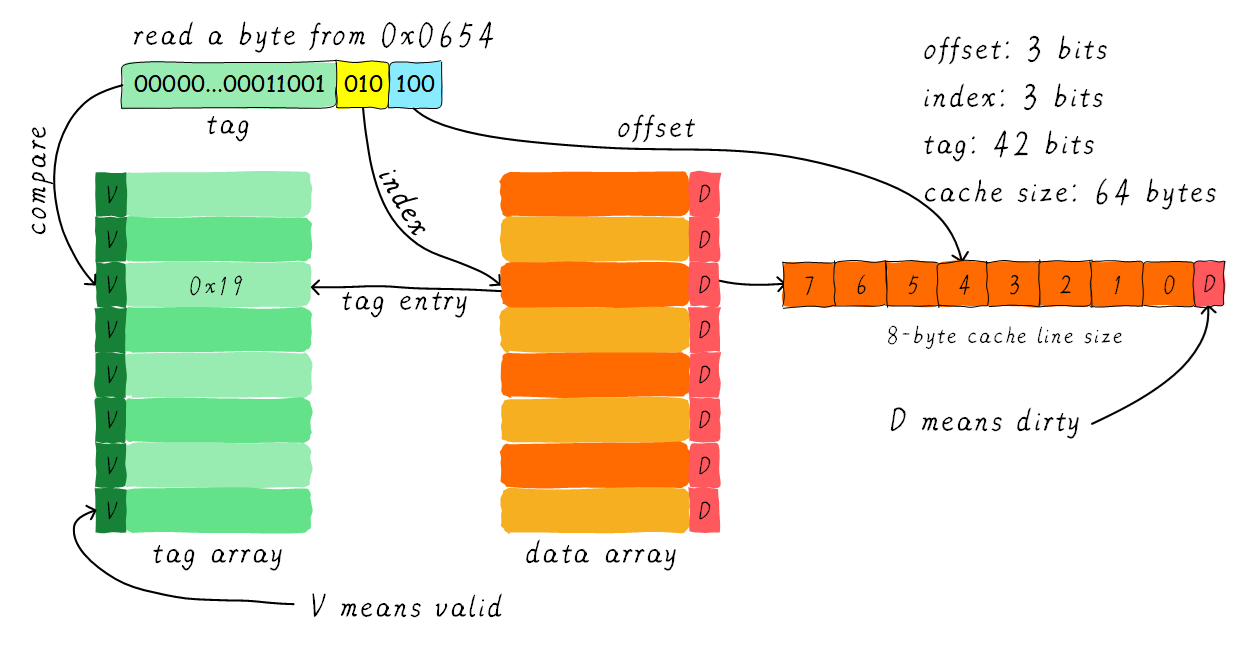

如图是最简单的缓存存取和命中判断示意。其中 0x0654 是 CPU 要求获得数据的地址值,分为三段,称为 tag, index 和 offset;左侧的整体绿色八行表格,为 tag array ,物理存储在 tag SRAM 中;右侧的整体橘色八行表格,为 data array ,物理存储在 cache SRAM 芯片中;而 cache line 对应 data array 中的一行,每行有 8 字节有效数据和一个标志位。

我们一共有8行cache line,cache line大小是8 Bytes。所以我们可以利用地址低3 bits(如上图地址蓝色部分)用来寻址8 bytes中某一字节,我们称这部分bit组合为offset。同理,8行cache line,为了覆盖所有行。我们需要3 bits(如上图地址黄色部分)查找某一行,这部分地址部分称之为index。现在我们知道,如果两个不同的地址,其地址的bit3-bit5如果完全一样的话,那么这两个地址经过硬件散列之后都会找到同一个cache line。所以,当我们找到cache line之后,只代表我们访问的地址对应的数据可能存在这个cache line中,但是也有可能是其他地址对应的数据。所以,我们又引入tag array区域,tag array和data array一一对应。每一个cache line都对应唯一一个tag,tag中保存的是整个地址位宽去除index和offset使用的bit剩余部分(如上图地址绿色部分)。tag、index和offset三者组合就可以唯一确定一个地址了。因此,当我们根据地址中index位找到cache line后,取出当前cache line对应的tag,然后和地址中的tag进行比较,如果相等,这说明cache命中。如果不相等,说明当前cache line存储的是其他地址的数据,这就是cache缺失。在上述图中,我们看到tag的值是0x19,和地址中的tag部分相等,因此在本次访问会命中。由于tag的引入,因此解答了我们之前的一个疑问“为什么硬件cache line不做成一个字节?”。这样会导致硬件成本的上升,因为原本8个字节对应一个tag,现在需要8个tag,占用了很多内存。

我们可以从图中看到tag旁边还有一个valid bit,这个bit用来表示cache line中数据是否有效(例如:1代表有效;0代表无效)。当系统刚启动时,cache中的数据都应该是无效的,因为还没有缓存任何数据。cache控制器可以根据valid bit确认当前cache line数据是否有效。所以,上述比较tag确认cache line是否命中之前还会检查valid bit是否有效。只有在有效的情况下,比较tag才有意义。如果无效,直接判定cache缺失。

在蜗窝科技的这段解释中,需要明确的一点是,图中右侧 8 bytes 的 cache line,每一个字节都真真切切存储着主存中的镜像数据。所以当 CPU 要求 0x0654 的数据时,该数据 就是 右侧 cache line 中编号 4 的字节的值。通过将主存中的数据镜像到存取速度更快的缓存中,使得 CPU 等待数据的时间缩短,提高整体计算效率。

最近的 CPU 设计自然是不会再将缓存裸露到核心封装之外,一般人也就无缘真正认识缓存和缓存 tag 的物理存在。到目前为止,新型的高速 CPU 都往往有三级缓存,包括一级的指令、数据缓存,二级本核主存混合缓存,三级核间共享混合缓存。

据知乎供图,一二三级缓存和主存的速度大致对比为 1TB/s : 300GB/s:150GB/s:20GB/s,延迟(纳秒)大致对比为 1:3:12:60。

好了,回炉奔二学习研究完毕。是把它挂起来当饰品看呢,还是把它原价闲鱼专卖,这是一个问题。